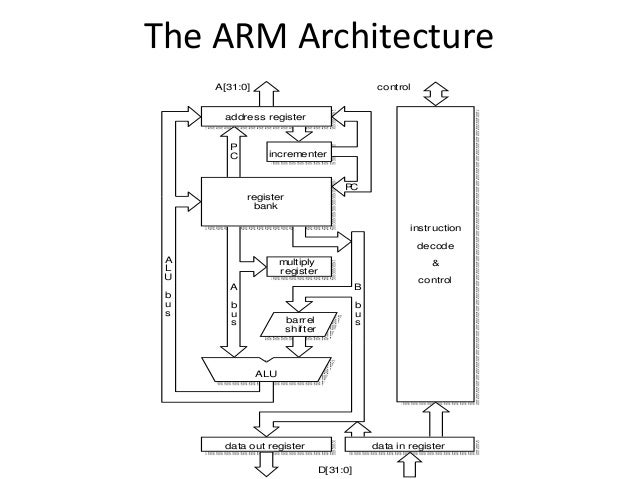

ARM Architecture

Similar RISC Design

- Reduced set/single cycle/fix length instructions

- One-stage decoding pipleline, no microcode

- A large set of GP registers

- 32 bit load-store architecture

With following differences

- Multiple-register load/store with variable cycle execution

- Inline barrel shift, leading to complex instructions

- 16 bit Thumb instructions

- Conditional execution

- DSP instructions

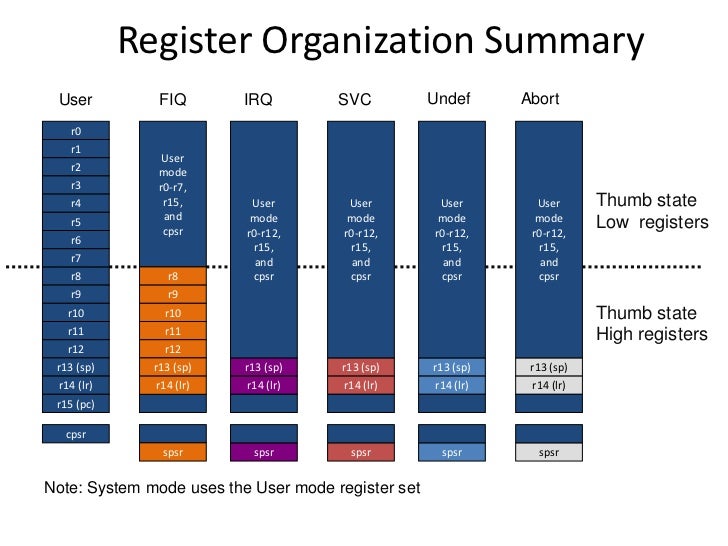

Processor Modes

Each mode has access to its own stack space and a different subset of registers - banked registers.

- User mode: The only non-privileged mode.

- FIQ mode: A privileged mode that is entered whenever the processor accepts a fast interrupt request.

- IRQ mode: A privileged mode that is entered whenever the processor accepts an interrupt.

- Supervisor (svc) mode: A privileged mode entered whenever the CPU is reset or when an SVC instruction is executed.

- Abort mode: A privileged mode that is entered whenever a prefetch abort or data abort exception occurs.

- Undefined mode: A privileged mode that is entered whenever an undefined instruction exception occurs.

- System mode (ARMv4 and above): The only privileged mode that is not entered by an exception. It can only be entered by executing an instruction that explicitly writes to the mode bits of the Current Program Status Register (CPSR) from another privileged mode (not from user mode).

- Monitor mode (ARMv6 and ARMv7 Security Extensions, ARMv8 EL3): A monitor mode is introduced to support TrustZone extension in ARM cores.

- Hyp mode (ARMv7 Virtualization Extensions, ARMv8 EL2): A hypervisor mode that supports virtualization

- Thread mode (ARMv6-M, ARMv7-M, ARMv8-M): A mode which can be specified as either privileged or unprivileged, while whether Main Stack Pointer (MSP) or Process Stack Pointer (PSP) is used can also be specified in CONTROL register with privileged access. This mode is designed for user tasks in RTOS environment but it's typically used in bare-metal for super-loop.

- Handler mode (ARMv6-M, ARMv7-M, ARMv8-M): A mode dedicated for exception handling (except the RESET which are handled in Thread mode). Handler mode always uses MSP and works in privileged level.

Register organization

Interrupts

AArch64

- Fixed 32 bit instruction width

- 31 64-bit GP registers: X0-X30 with 32-bit subregisters W0-W30, +SP, +PC +ZR

- FPU with 32 registers, each 128-bit wide

- 64-bit addresses

- paired load/store, no STM/LDM

References

- https://www.youtube.com/watch?v=7LqPJGnBPMM

- https://www.csie.ntu.edu.tw/~cyy/courses/assembly/12fall/lectures/handouts/lec08_ARMarch.pdf

- https://en.wikipedia.org/wiki/ARM_architecture

- https://events.static.linuxfound.org/images/stories/pdf/lcna_co2012_marinas.pdf

No comments:

Post a Comment